This List of IEEE Milestones documents the over 150 IEEE Milestones that have been dedicated around the world.

Region 6 Milestones

– SFBAC

SFBAC Milestones:

IEEE Milestones Dedicated Within the San Francisco Bay Area Council (SFBAC)

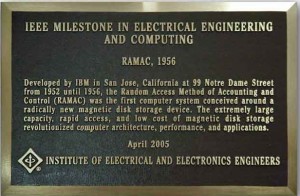

| RAMAC, 1956: San Jose, CA; Dedicated 26 May 2005 – Santa Clara Valley Section

Developed by IBM in San Jose, California at 99 Notre Dame Street from 1952 until 1956, the Random Access Method of Accounting and Control (RAMAC) was the first computer system conceived around a radically new magnetic disk storage device. The extremely large capacity, rapid access, and low cost of magnetic disk storage revolutionized computer architecture, performance, and applications. |

|

| Semiconductor Planar Process and Integrated Circuit, 1959: Palo Alto, CA; Dedicated 8 May 2009 – Santa Clara Valley Section

The 1959 invention of the Planar Process by Jean A. Hoerni and the Integrated Circuit (IC) based on planar technology by Robert N. Noyce catapulted the semiconductor industry into the silicon IC era. This pair of pioneering inventions led to the present IC industry, which today supplies a wide and growing variety of advanced semiconductor products used throughout the world. |

|

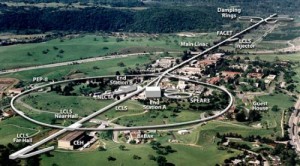

| Stanford Linear Accelerator Center, 1962: Menlo Park, CA; Dedicated February 1984 – San Francisco Bay Area Council (ASME National Historic Engineering Landmark, jointly designated with IEEE)

The Stanford two-mile accelerator, the longest in the world, accelerates electrons to the very high energy needed in the study of subatomic particles and forces. Experiments performed here have shown that the proton, one of the building blocks of the atom, is in turn composed of smaller particles now called quarks. Other research here has uncovered new families of particles and demonstrated subtle effects of the weak nuclear force. This research requires the utmost precision in the large and unique electromechanical devices and systems that accelerate, define, deliver and store the beams of particles, and in the detectors that analyze the results of the particle interactions.

|

|

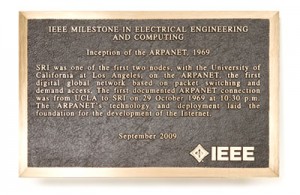

| Inception of the ARPANET, 1969: Menlo Park, CA; Dedicated 16 September 2009 – Santa Clara Valley Section

SRI was one of the first two nodes, with the University of California at Los Angeles, on the ARPANET, the first digital global network based on packet switching and demand access. The first documented ARPANET connection was from UCLA to SRI on 29 October 1969 at 10:30 p.m. The ARPANET’s technology and deployment laid the foundation for the development of the Internet. |

|

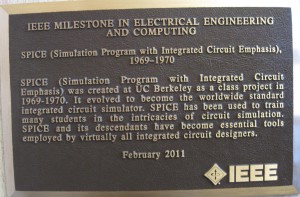

| Birth of the SPICE Circuit Simulation Program, 1971: Berkeley, CA; Dedicated 20 February 2011 – Santa Clara Valley Section and Oakland East Bay Section

SPICE (Simulation Program with Integrated Circuit Emphasis) was created at UC Berkeley as a class project in 1969-1970. It evolved to become the worldwide standard integrated circuit simulator. SPICE has been used to train many students in the intricacies of circuit simulation. SPICE and its descendents have become essential tools employed by virtually all integrated circuit designers. |

|

| Development of the HP-35, the First Handheld Scientific Calculator, 1972: Palo Alto, CA; Dedicated 14 April 2009 – Santa Clara Valley Section

The HP-35 was the first handheld calculator to perform transcendental functions (such as trigonometric, logarithmic and exponential functions). Most contemporary calculators could only perform the four basic operations – addition, subtraction, multiplication, and division. The HP-35 and subsequent models have replaced the slide rule, used by generations of engineers and scientists. The HP-35 performed all the functions of the slide rule to ten-digit precision over a full two-hundred-decade range. |

|

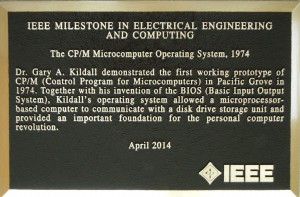

| The CP/M Microcomputer Operating System, 1974: Pacific Grove, CA; Dedicated 25 April 2014 – Santa Clara Valley Section

Dr. Gary A. Kildall demonstrated the first working prototype of CP/M (Control Program for Microcomputers) in Pacific Grove in 1974. Together with his invention of the BIOS (Basic Input Output System), Kildall’s operating system allowed a microprocessor-based computer to communicate with a disk drive storage unit and provided an important foundation for the personal computer revolution. |

|

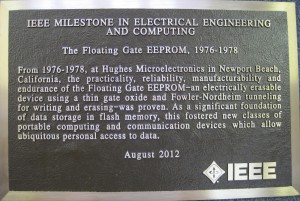

| The Floating Gate EEPROM, 1976-1978: Milpitas, CA; Dedicated 20 August 2012 – Santa Clara Valley Section

From 1976-1978, at Hughes Microelectronics in Newport Beach, California, the practicality, reliability, manufacturability and endurance of the Floating Gate EEPROM — an electrically erasable device using a thin gate oxide and Fowler-Nordheim tunneling for writing and erasing — was proven. As a significant foundation of data storage in flash memory, this fostered new classes of portable computing and communication devices which allow ubiquitous personal access to data. |

|

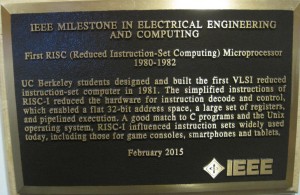

| First RISC (Reduced Instruction-Set Computing) Microprocessor, 1980-1982: Berkeley, CA; Dedicated 12 February 2015 – Oakland East Bay Section

UC Berkeley students designed and built the first VLSI reduced instruction-set computer in 1981. The simplified instructions of RISC-I reduced the hardware for instruction decode and control, which enabled a flat 32-bit address space, a large set of registers, and pipelined execution. A good match to C programs and the Unix operating system, RISC-I influenced instruction sets widely used today, including those for game consoles, smartphones and tablets. |

|

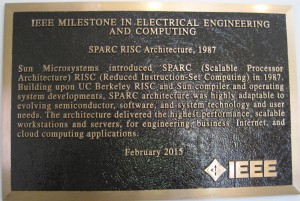

| SPARC RISC Architecture, 1987: Santa Clara, CA; Dedicated 13 February 2015 – Santa Clara Valley Section

Sun Microsystems introduced SPARC (Scalable Processor Architecture) RISC (Reduced Instruction-Set Computing) in 1987. Building upon UC Berkeley RISC and Sun compiler and operating system developments, SPARC architecture was highly adaptable to evolving semiconductor, software, and system technology and user needs. The architecture delivered the highest performance, scalable workstations and servers, for engineering, business, Internet, and cloud computing applications. |

|